555 TIMER/ TRIPLE FIVE TIMER PIN OUT AND FREQUENCY DETERMINATION

This tutorial provides sample circuits to set up a 555 timer in monostable, astable, and bistable modes as well as an in depth discussion of how the 555 timer works and how to choose components to use with it. The 555 timer is a chip that can be used to create pulses of various durations, to output a continuous pulse waveform of adjustable pulse width and frequency, and to toggle between high and low states in response to inputs. By wiring the 555 timer with resistors and capacitors in various ways, you can get it to operate in three different modes

Monostable Mode is great for creating time delays. In this mode an external trigger causes the 555 timer to output a pulse of an adjustable duration.

Astable Mode outputs an oscillating pulse signal/waveform. In this mode the output of the 555 timer is switching between high and low states at a tunable frequency and pulse width.

Bistable Mode causes the 555 timer to toggle its output between high and low states depending on the state of two inputs.

Some applications that come to mind include:

- a steady clock/trigger to keep time in a circuit (astable mode)

- the core oscillator of an analog synthesizer, with the addition of some op amps and other components this pulse wave can be shaped into a triangle, saw, and even sine shapes

- a very basic chiptune style noise maker (see atari punk console)

- time delay for an incoming signal (monostable mode)

- very basic storage of input data/management of two button control system (bistable mode)

The 555 timer is flexible, cheap, and easy to find (you can even pick them up at Radioshack). It's also a great starting point for audio projects because its output can be wired directly to a speaker. Feel free to use any of the info or example circuits I've provided in this tutorial as a starting point for an entry in the DIY Audio Contest! We're giving away an HDTV, DSLR cameras and tons of other great stuff! (ends November 26)

Pin diagram is as follows:

figures above shows the pin connections to the 555 timer, it was take directly from the 555 timer datasheet. The power connections to the chip are through pins 1 (ground) and 8 (+Vcc). The positive supply voltage (+Vcc) should be between 5 and 15V.

The second image is a close up of the diagram depicting the internal functional components of the chip. This consists of a few different elements: resistors, transistors, comparators, a flip flop, and an output stage.

All three resistors diagrammed in fig 2 are 5kOhm (see image notes in fig 3). The purpose of these resistors is to set up a voltage divider between Vcc and ground. Since all resistors are the same value we know that the voltage at the junction between the resistors are 2/3Vcc and 1/3Vcc (see image notes in fig 2). These voltages are used as reference voltages for the comparators

A comparator is a circuit which compares an input with a reference voltage and outputs a LOW or HIGH signal based on whether the input is a higher or lower voltage than the reference. The 555 timer uses several transistors to construct its comparators (see the image notes in fig 3), so in the simplified functional diagram in fig 2 they are represented by boxes labelled "comparator." The comparator connected to pin 2 compares the "trigger" input to a reference voltage of 1/3Vcc and the comparator connected in pin 6 compares the "threshold" input to a reference voltage of 2/3Vcc from the voltage divider.

A flip flop is circuit that switches between two stable states based on the state of its inputs. The 555 flip flop outputs a high or low based on the states of the two comparators. When the trigger comparator is outputting a low signal (regardless of the state of the threshold comparator), the flip flop switches high, when both comparators are outputting a high signal, the flip flop switches low. The timing of a high pulse output from the flip flop can also be manually reset (the beginning of a pulse can be triggered) by pulsing the reset pin low.

The functional diagram in fig 2 also includes two transistors. The transistor attached to pin 7 is an NPN transistor. Since pin 7 is connected to the collector pin of the NPN transistor, this type of configuration is called open collector or open drain. This pin is usually connected to a capacitor and is used to discharge the capacitor each time the output pin goes low. The transistor attached to pin 4 is a PNP transistor. The purpose of this transistor is to buffer the reset pin, so the 555 does not source current from this pin and cause it to sag in voltage.

The output stage of the 555 timer is indicated in the image notes of fig 3. Its purpose is to act as a buffer between the 555 timer and any loads that may be attached to its output pin. The output stage supplies current to the output pin so that the other functional component of the 555 timer don't have to.

Frequency determination

When using in astable state:

calculations:

In the astable mode, the frequency of the pulse stream depends on the values of R1, R2 and C:

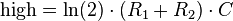

The high time from each pulse is given by:

The power capability of R1 must be greater than

.

.Note:

Particularly with bipolar 555s, low values of R1 must be avoided so that the output stays saturated near zero volts during discharge, as assumed by the above equation. Otherwise the output low time will be greater than calculated above. It should be noted that the first cycle will take appreciably longer than the calculated time, as the capacitor must charge from 0V to 2/3 of VCC from power-up, but only from 1/3 of VCC to 2/3 of VCC on subsequent cycles.

The circuit configuration above does not permit a duty cycle of less than 50%, because the time-constant for charging C1 is always greater than for discharging. To achieve any arbitrary duty cycle, R2 can be moved to be in series with pin 7, the discharge pin. The duration of the high-output interval (during the charging of C1) is then 0.693(R1C1), and the low-output interval (while discharging C1) is 0.693(R2C1). The total time period, T, is 0.693(R1+R2)C1. [8]

In order to achieve a duty cycle of less than 50%, a diode (that is fast enough for the application) can be added in parallel with R2, with the anode on the capacitor side. This bypasses R2 during the high part of the cycle so that the high interval depends approximately only on R1 and C. The presence of the diode is a voltage drop that slows charging on the capacitor so that the high time is longer than the expected and often-cited ln(2)*R1C = 0.693 R1C. The low time will be the same as without the diode as shown above. With a diode, the high time is

The operation of RESET in this mode is not well defined, some manufacturers' parts will hold the output state to what it was when RESET is taken low, others will send the output either high or low.

Comments